## "L'avenir est comme le reste il n'est plus ce qu'il était'

Paul Valery, "Notre Destin et Les Lettres", 1937)"

Yan Borodovsky

SPIE Fellow

### The Future isn't what is used to be

Yan Borodovsky

SPIE Fellow

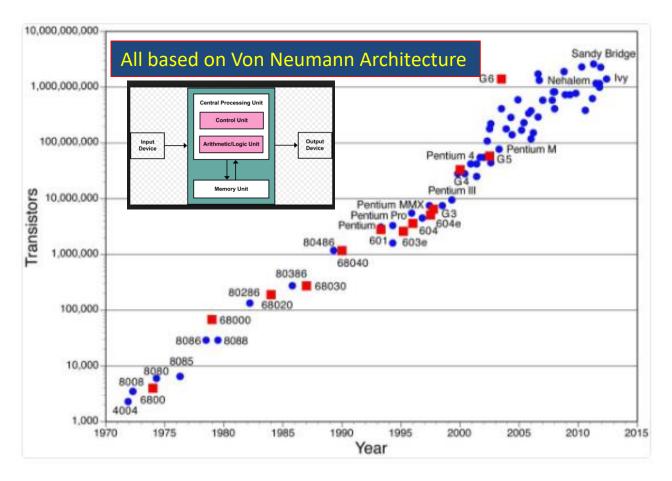

### Moore's Law that used to be...

Moore's law Graph Source:

"What lies beneath? 50 years of enabling Moore's Law", Mike Czerniak, Solid State Technology, Nov. 17, 2015

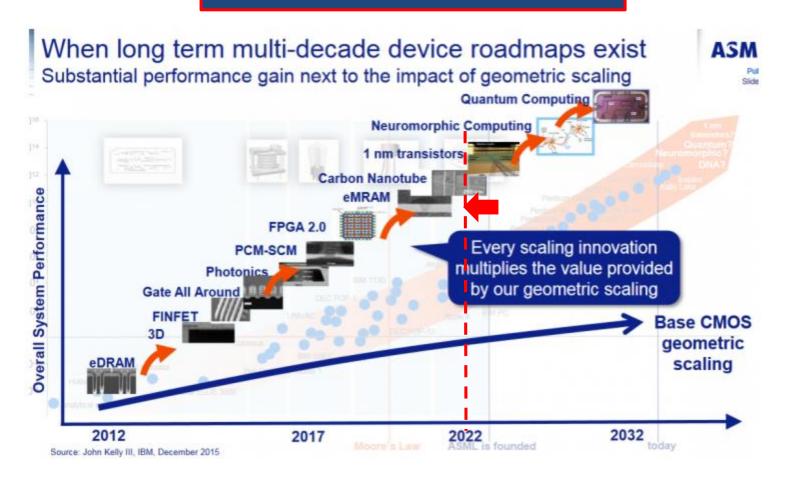

### Moore's Law to be

Von Neumann AND Non-Von Neumann

### 2022-2024 Computing Platforms

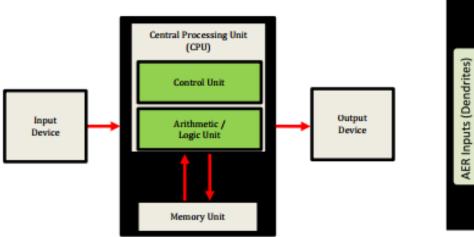

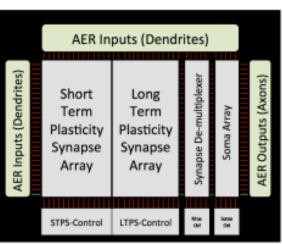

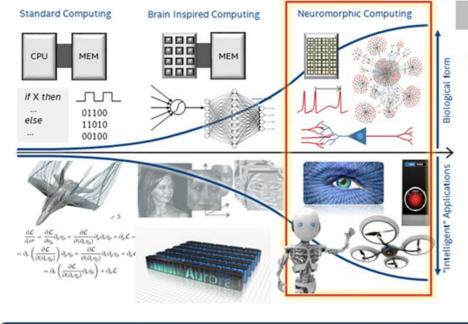

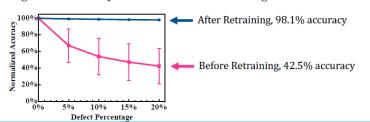

#### von Neumann Architecture

#### Neuromorphic Architecture

Figure 1. Comparison of high-level conventional and neuromorphic computer architectures. The socalled "von Neumann bottleneck" is the data path between the CPU and the memory unit. In contrast, a neural network based architecture combines synapses and neurons into a fine grain distributed structure that scales both memory (synapse) and compute (soma) elements as the systems increase in scale and capability, thus avoiding the bottleneck between computing and memory.

**Source:** "Neuromorphic Computing: From Materials to Systems Architecture"

Report of a Roundtable Convened to Consider Neuromorphic Computing Basic Research Needs, October 29-30, Gaithersburg, MD, USA, US DOE, Office of Scince

https://science.energy.gov/~/media/bes/pdf/reports/2016/NCFMtSA rpt.pdf

## Von Neumann AND Non-Von Neumann already here

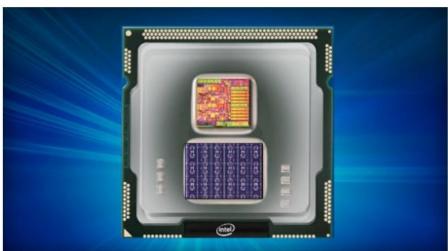

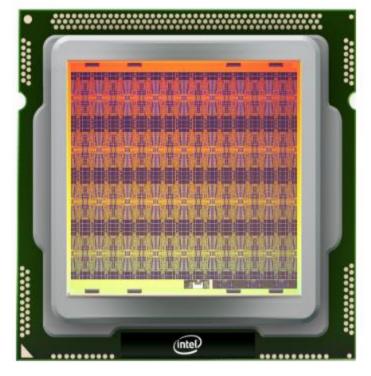

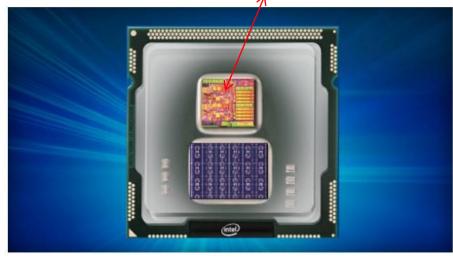

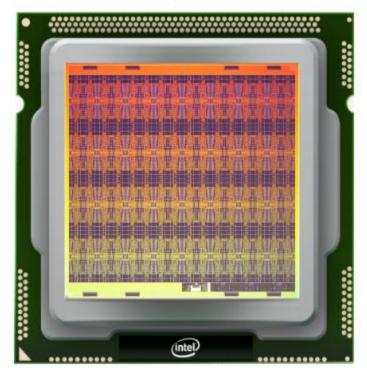

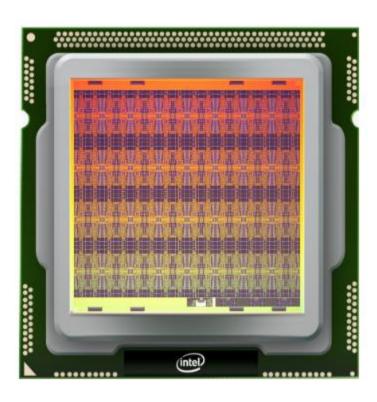

#### Intel Unveils Neuromorphic, Self-Learning Chip Codenamed Loihi

Loihi simulates a total of 130,000 neurons and 130 million synapses, all capable of communicating with each other... comparable to some small insects. For example, a common fruit fly, an insect studied for AI research, has about 250,000 neurons and 10 million synapses. ...human brain - 100 billion neurons,

https://www.extremetech.com/computing/256467-intel-unveils-new-neuromorphic-self-learning-chip-codenamed-loihi

## Von Neumann AND Non-Von Neumann already here

#### Intel Unveils Neuromorphic, Self-Learning Chip Codenamed Loihi

By Joel Hruska on September 27, 2017 at 9:18 am 14 Comments

This is Control Programming Unit >50% area is defect intolerant

Loihi simulates a total of 130,000 neurons and 130 million synapses, all capable of communicating with each other... comparable to some small insects. For example, a common fruit fly, an insect studied for AI research, has about 250,000 neurons and 10 million synapses. ...human brain - 100 billion neurons,

This is Neuromorphic Part and it is (or will be) defect tolerant

https://www.extremetech.com/computing/256467-intel-unveils-new-neuromorphic-self-learning-chip-codenamed-loihi

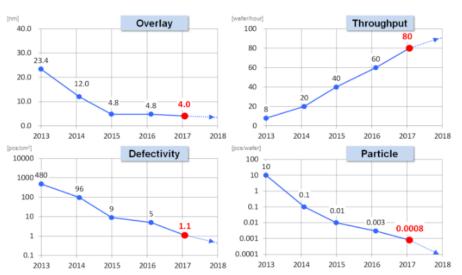

## Big 2017 Story – EUV Ecosystem status gives enough confidence to customers to place multiple tools orders

## EUV shipments ramp in support of customers' production plans

#### **ASML**

Public Slide 16 January 17, 2018

#### Customers

show commitment to insert EUV in volume manufacturing by ordering systems

- 4 EUV systems shipped in Q4, 5 recognized in revenue

- Of the 12 EUV shipments planned in 2017, we shipped 10 during the year, 1 shipment is in progress, 1 shipment planned in January 2018

- 10 orders received, EUV backlog increased to 28

- Planned shipments of 22 systems in 2018, back-end loaded, and plan at least 30 systems in 2019

#### **ASML**

commits to securing system performance, shipments and support required for volume manufacturing

For volume manufacturing of logic and memory, ASML remains committed to deliver:

- Throughput of >125 wafers per hour

- Availability of >90% on average

- Shipments on time in sufficient volume

- Ability to support a growing installed base

Source: https://staticwww.asml.com/doclib/investor/financial results/2018/asml 20180107 presentation.pdf

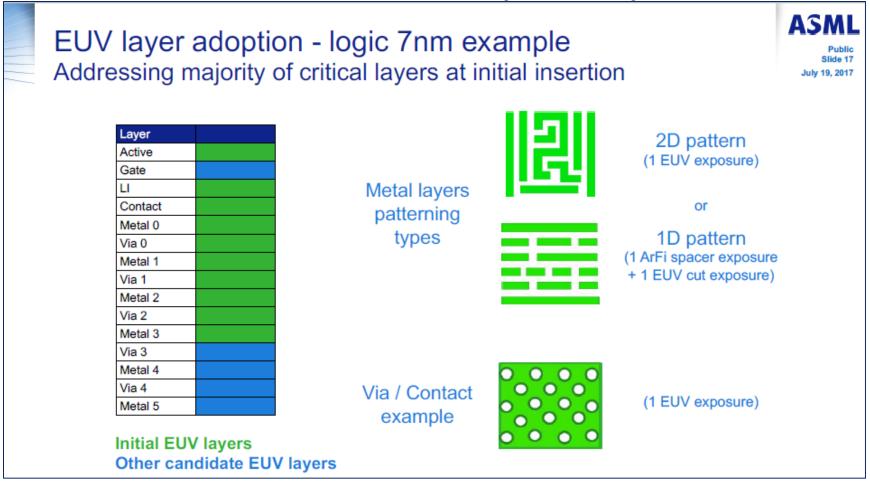

## Foundries -7nm(+, ++) EUV

Source: ASML 2017 Second-Quarter Results Webcast Presentation

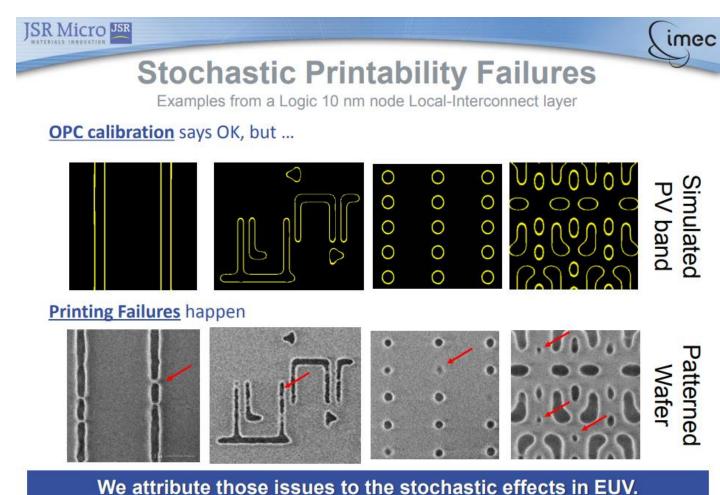

## Stochastic Patterning Failures must be eliminated for EUV HVM

Oct 27, 2014 Washington, D.C.

2014 International Symposium on Extreme Ultraviolet Lithography

2

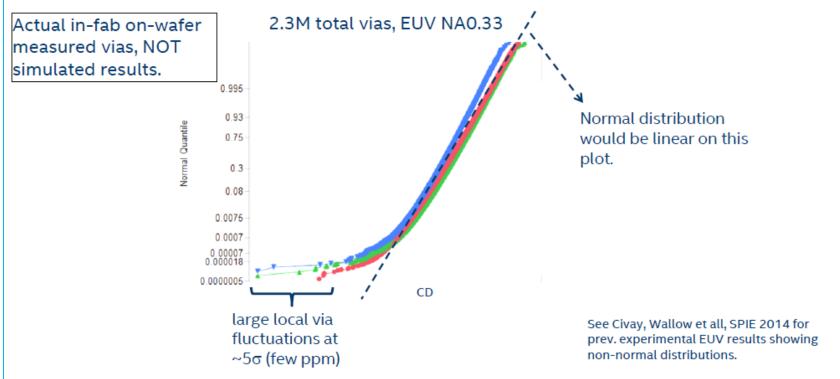

## With 10B Via/Cuts per chip 5σ process will kill every chip – zero yield

### 2.3M measured vias: Non-normal CD distribution.

R. Bristol

SPIE Advanced Lithography, Feb 2017

## Via Patterning with EUV Stochastic requirements for vias

Required failure rate for 99% die yield

|                         | 26X32mm die     |                         |                        |               |  |  |

|-------------------------|-----------------|-------------------------|------------------------|---------------|--|--|

| NA = 0.33 Illum.        | $HP_{min}$ (nm) | Via count               | Fail.rate              | <b>π</b> ~7σ  |  |  |

| quad with $\sigma$ =0.2 | 26              | 0.18 x 10 <sup>11</sup> | 55 x 10 <sup>-14</sup> |               |  |  |

| 0.33 NA Limit           | 18              | 0.39 x 10 <sup>11</sup> | 26 x 10 <sup>-14</sup> |               |  |  |

| 0.55NA Limit            | 11              | 1.03 x 10 <sup>11</sup> | 10 x 10 <sup>-14</sup> | <b>7</b> ~8 σ |  |  |

| YB 2/26/2018            | 8               | 1.95 x 10 <sup>11</sup> | 5 x 10 <sup>-14</sup>  |               |  |  |

CXR((iii)

Berkeley Lab | MSD Materials Sciences Division

5

#### Measuring and Modeling Stochastic Limitations in EUV Resists

P. Naulleau,

W. Chao, O. Kostko, F. Ogletree, Berkeley Lab

S. Bhattaria, A. Neureuther, UC Berkeley

Photopolymer Japan, Chiba, Japan, June 26 - 29, 2017

## Photon Shot Noise AND Resist Inhomogeneity produce Stochastic Noise in Litho Channel

#### Modeling Via stochastics: resist conditions

Baseline Chemically Amplified Resist used in subsequent slides:

Esize =  $79 \text{ mJ/cm}^2$

$E0 = 15.7 \text{ mJ/cm}^2$

QE = 3

$PAG = 0.2/nm^{3}$

Quencher = 0.085/nm<sup>3</sup>

Protecting groups = 2/nm<sup>3</sup>

Absorptivity = 4.2/um

Thickness = 35 nm

Acid diffusion range = 12 nm

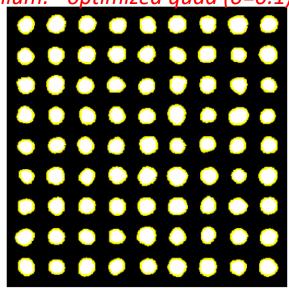

16-nm HP contacts; NA = 0.33 Illum. - optimized quad ( $\sigma$ =0.1)

Developed resist

Measuring and Modeling Stochastic Limitations in EUV Resists

P. Naulieau, W. Chao, O. Kostko, F. Ogletree, Berkeley Lab S. Bhattaria, A. Neureuther, UC Berkeley

Photopolymer Japan, Chiba, Japan, June 26 - 29, 2017

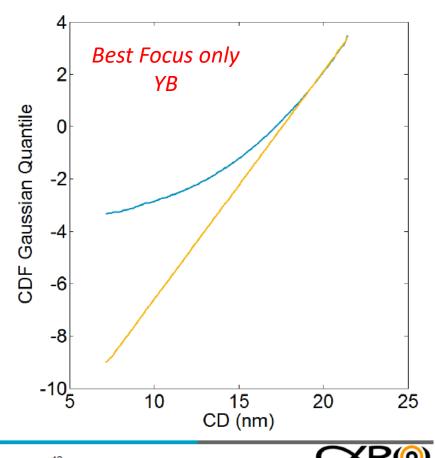

## Stochastic Noise in the Channel is Significant - parts per several millions

CDF shows large variations at  $4\sigma$  frequency

> CDF of stochastic resist model

Gaussian CDF

Berkeley Lab | MSD Materials Sciences Division

12

## Via Patterning with EUV Stochastic requirements for vias

Required failure rate for 99% die yield

26X32mm die

| Year | Node  | EUV       | $HP_{min}$ (nm) | Via count               | Fail.rate              | 7 -           |

|------|-------|-----------|-----------------|-------------------------|------------------------|---------------|

| 2019 | ~7nm  | 1X        | 26              | 0.18 x 10 <sup>11</sup> | 55 x 10 <sup>-14</sup> | ~7 σ          |

| 2020 | 5nm   | 2X        | 18              | 0.39 x 10 <sup>11</sup> | 26 x 10 <sup>-14</sup> |               |

| 2022 | 3nm   | <i>3X</i> | 11              | 1.03 x 10 <sup>11</sup> | 10 x 10 <sup>-14</sup> | <b>~</b> ~8 ~ |

| 2026 | 1.5nm | ?         | 8               | 1.95 x 10 <sup>11</sup> | 5 x 10 <sup>-14</sup>  | ~8 σ          |

YB

Berkeley Lab | MSD Materials Sciences Division

## BERKELEY LAB CXR(0)

5

#### Measuring and Modeling Stochastic Limitations in EUV Resists

P. Naulleau.

W. Chao, O. Kostko, F. Ogletree, Berkeley Lab

S. Bhattaria, A. Neureuther, UC Berkeley

Photopolymer Japan, Chiba, Japan, June 26 - 29, 2017

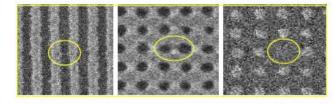

#### EUV RESIST PERFORMANCE LOW DOSE IS ACHIEVED, BUT LIMITED BY STOCHASTICS

| Feature                             |      | pitch<br>pace / Vertical |     | pitch<br>ace / Vertical |     | pitch<br>ce / Horizontal | 36nm pitch<br>regular dense<br>contacts | 38nm pitch<br>regular dense<br>pillars |

|-------------------------------------|------|--------------------------|-----|-------------------------|-----|--------------------------|-----------------------------------------|----------------------------------------|

| Resist<br>type                      | CAR  | NCAR                     | CAR | NCAR                    | CAR | NCAR                     | CAR                                     | NCAR                                   |

| SEM<br>top-down<br>image<br>@ BE/BF | •    | <b>)</b>                 | •   | *<br>*                  |     |                          |                                         |                                        |

| Dose<br>mJ/cm²                      | 30.5 | 31.4                     | 21  | 20.9                    | 39  | 37.3                     | 31                                      | 30                                     |

| LWR/LCDU<br>nm                      | 4.7  | 4.6                      | 5.4 | 5.2                     | 4.5 | 4.2                      | 3.5                                     | 3.9                                    |

Challenge #1: Stochastic Failures

ımec

#### Source:

#### **EUV DEVELOPMENTS AT IMEC**

DANILO DE SIMONE, PETER DE BISSCHOP, IVAN POLLENTIER, WAIKIN LI, EMILY GALLAGHER, VICKY PHILIPSEN, VINCENT WIAUX, RYOUNG-HAN KIM, ERIC HENDRICKX, GEERT VANDENBERGHE, KURT RONSE, <u>GREG MCINTYRE</u> ON BEHALF OF IMEC PATTERNING

15 JUNE 2017, EUVL WORKSHOP, BERKELEY, CA

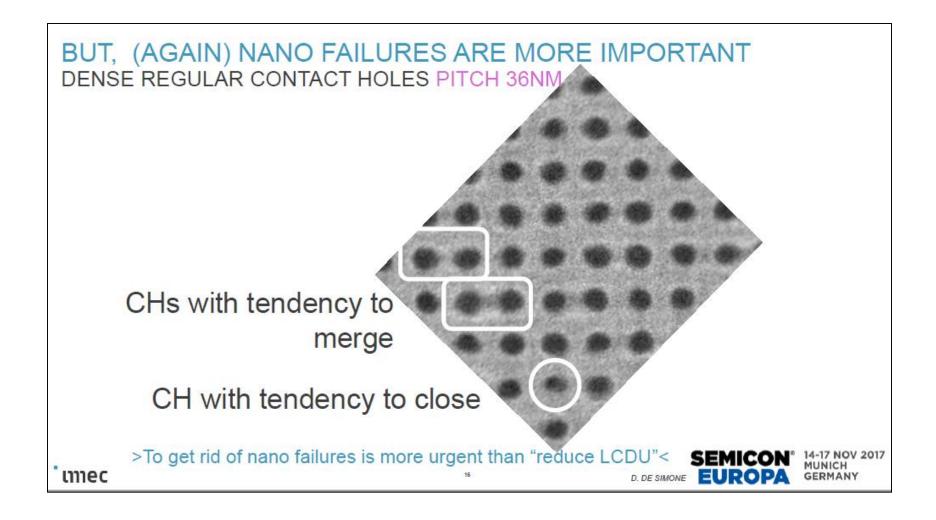

Features Patterned with NXE 3300 NA=0.33

#### Stochastic Nanofailures

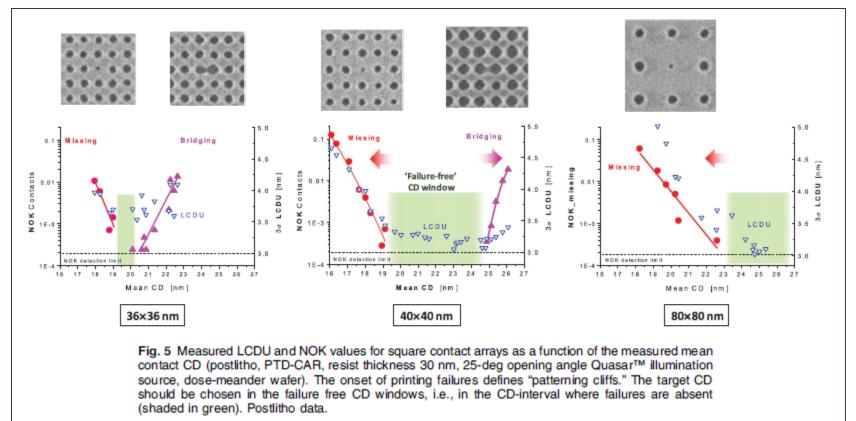

## Yield and Stochastic Failures 5nm Node

Source: Peter De Bisschop, "Stochastic effects in EUV lithography: random, local CD variability, and printing failures," J. Micro/Nanolith. MEMS MOEMS 16(4), 041013 (2017), doi: 10.1117/1.JMM.16.4.041013.

Defectivity Intolerance of Von Neumann Computing will eventually result in end of viable area scaling.

## Patterning Holy Grail

Moore's Law = Density+Cost Per Transistor

$CPT_{n+1/n}$ =Wafer  $Cost_{n+1/n}$ \*AreaScale<sub>n+1/n</sub>

/Accuming any include

|            | n+1/n      |     |

|------------|------------|-----|

| Wafer Cost | Area Scale | CPT |

| 1.1        | 0.55       | 0.6 |

| 1.2        | 0.50       | 0.6 |

| 1.3        | 0.46       | 0.6 |

| 1.4        | 0.43       | 0.6 |

| 1.5        | 0.40       | 0.6 |

| 1.4        | 0.43       | 0.6 |

Snm Node and below will be progressively defect prone due to impact of Stochastic effects in EUV Litho.

Defects ↑ = Yield √

$CPT_{n+1/n} = 2*PatternCost_{n+1/n}*AreaScale_{n+1/n}$

Lowest PatterningCost\*AreaScale solution is Litho Holy Grail.

Y.Borodovsky, Alternative Lithographic Technologies VII, Conference 9423, 23 February 2015, San Jose, CA, USA

17

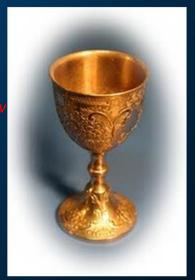

### Bioinspired Computing will be a vehicle to get Through Defect Limiting Moore's Law Wall

Source

"The future of electronics based on memristive systems"

Mohammed A. Zidan, John Paul Strachan & Wei D. Lu

Nature Electronics 1, 22–29 (2018),doi:10.1038/s41928-017-0006-8

### Beyond von Neumann Computing – Opportunity for further scaling with 10<sup>X</sup> defect density

#### Efficient & Scalable Neuromorphic Systems

Neuromorphic Circuit – circuit that in its structure mimics organization of the brain

#### Implementation Features

Spatio-temporal encoding Distributed memory/compute Complex & efficient network Dynamic connectivity Asynchronous/event-driven Continuous learning Synaptic plasticity Homeostasis Stochasticity Recurrent Adaptive & resilient

Exploit integration, spike timing, sparsity, plasticity & resiliency

"Challenges and Opportunities for Efficient & Scalable Neuromorphic Systems", Vivek De, Intel, DAC54, 6/18-22/2017. Austin, TX USA

# Computing Under Large Perturbations and Uncertainties Neuromorphic Logic Networks and Robust Stochastic

### Bioinspired Computing might be a vehicle to get Through Defect Limiting Moore's Law Wall

Neuromorphic Circuit mimic in its structure organization of the brain

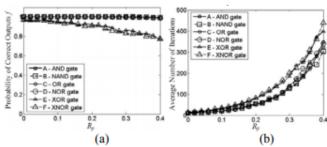

Figures 1 illustrate the quantitative data for the neuromorphic model of AND, NAND, OR, NOR, XOR and XNOR gates. The graph shows the relationship between  $R_p$  and probability (assurance) of reaching the correct solution, which is the supposed output of logic functions f. The stochastic perturbations  $\xi$  are modeled as uniformly distributed discrete random noise. For  $R_p \in [0\ 0.4]$ , the correct output f for AND, NAND, NOR and OR gates is achieved within ~100% requiring 400 iterations. In contrast, gates XOR and XNOR achieve the correct f from 80% to 100% requiring ~450 iterations. As  $R_p$  increases, the required number of iterations to achieve stability increases. Figure 1.b illustrates the number of iterations for the network to evolve to a stable state for different  $R_p$ .

Figure 1. Fault-tolerance of the neuromorphic model of elementary logic gates in the presence of disturbances for  $R_p \in [0.0.4]$  (5000 runs)

The superposition of inherent noise, interference and other disturbances are considered as stochastic perturbations  $\boldsymbol{\xi}$ . We use the perturbed-to-unperturbed ratio  $R_p$  which characterizes the *strength* of the  $\boldsymbol{\xi}$ . In general,  $\boldsymbol{\xi}$  is a mapping of all  $\xi_i$  which are hardware-dependent. Continuous and discrete distributions of random  $\xi_i$  result in probability functions  $\gamma(\xi_i)$  as well as distribution functions. Normal, binomial, hypergeometric, Poisson and other distributions affect  $\boldsymbol{\xi}$ .

We simplify the analysis by using  $R_p \in [0 \ 1]$ .

For an ideal unperturbed model  $R_p=0$ , while for a completely faulty cell,  $R_p=1$ .

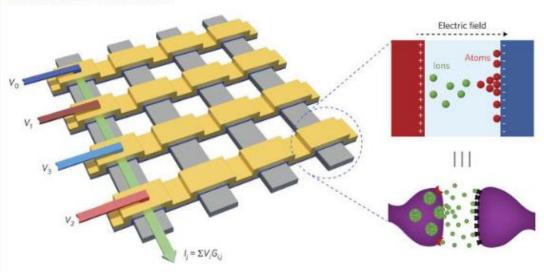

## RRAMs, Spin-Torque and other technologies are actively pursued as neuromorphic computing fundamental building blocks

### Hardware implementation of artificial neural networks in a memristor crossbar.

A memristor is formed at each crosspoint and can be used to simultaneously store data and process information. In this approach, vector-matrix multiplication can be obtained through Ohm's law and Kirchhoff's law through a simple read operation. In addition, the internal dynamics of memristors can be utilized to faithfully emulate underlying processes in biological synapses.  $V_i$ , voltage applied at row i;  $I_j$ , current through column j;  $G_{i,j}$ , conductance of the memristor at the intersection of row i and column j.

The future of electronics based on memristive systems" Mohammed A. Zidan, John Paul Strachan & Wei D. Lu *Nature Electronics* **1**, 22–29 (2018),doi:10.1038/s41928-017-0006-8

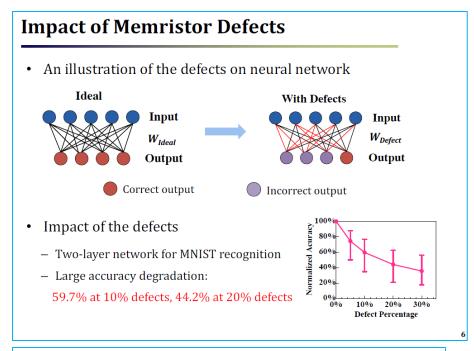

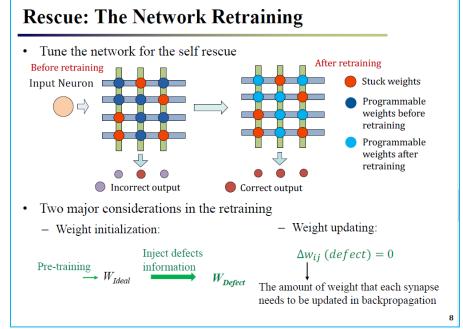

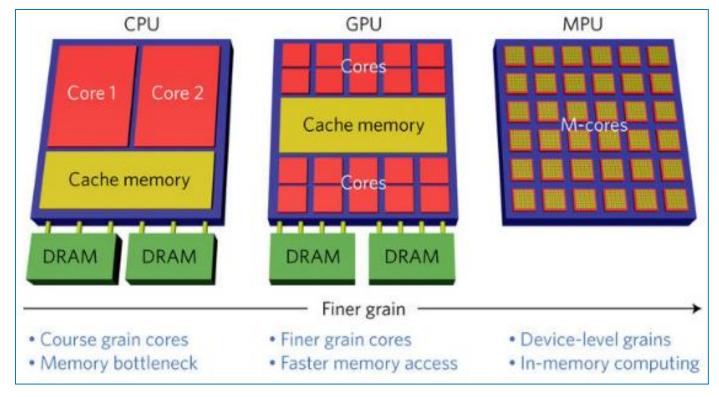

## Neuromorphic computing as enabler to break through next Moore's Law Wall

#### **Evaluations: Robustness of the Retraining**

- Feed-forward neural networks for MNIST recognition

- Recognition accuracy before and after retraining

Source: Prof. Chenchen Liu Presentation at DAC 17 "Rescuing Memristor-based Neuromorphic Design with High Defects"

Chenchen Liu, \* Miao Hu, \* John Paul Strachan and † Hai (Helen) Li; Clarkson University\*Hewlett-Packard Labs †Duke University

Full Paper: DAC '17, June 18-22, 2017, Austin, TX, USA c 2017 ACM. ISBN 978-1-4503-4927-7/17/06. . . \$15.00 DOI: http://dx.doi.org/10.1145/3061639.3062310

## Proposed MPU Architecture

**Source:** "The future of electronics based on memristive systems" Mohammed A. Zidan, John Paul Strachan & Wei D. Lu

Nature Electronics 1, 22–29 (2018),doi:10.1038/s41928-017-0006-8

## Proposed MPU Architecture shall support defect prone IC scaling

BM

#### High defect tolerance And reliability

Defect tolerance –

Treatment at the defective core is performed on other

Cores

Neuron Syrapses

Reliability – The majority voting system can be configured by programming

From "Neuromophic device for Automotive" by Yoshifumi Sakamoto, Engineering and Cognitive Innovation, IBM Japan, LTD, email: sakay@jp.ibm.com

### Putting it all in Perspective

Von Neumann Computing will eventually hit scaling wall as defectivity required to support it will reach  $< 10^{-14}$ /die features for overall  $10^{-2}$ /cm2 defects per wafer/per print.

Neuromorphic Computing can tolerate up to 4\*10<sup>-1</sup> defects per network.

Multiple technologies that were under development and commercialization efforts for >10 years but were not adopted for Logic will become viable alternatives to EUV to drive parts density and cost as per Moore's Law

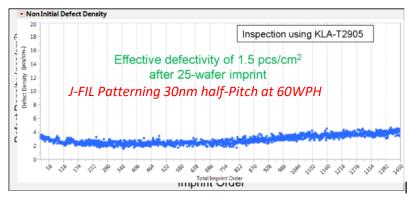

#### NanoImprint for Logic

From "A review of nanoimprint lithography for high-volume semiconductor device manufacturing" by Douglas J. Resnick/Jin Choi,

Advanced Optical Technologies, Volume 6, Issue 3-4, 2017

Figure 10. Defect density across a 25 wafer run. Overall defectivity increased by 1.5 defects/cm2.

NIL – OK to support Neuromorphic parts manufacturing now?

How will it scale during next 10 years?

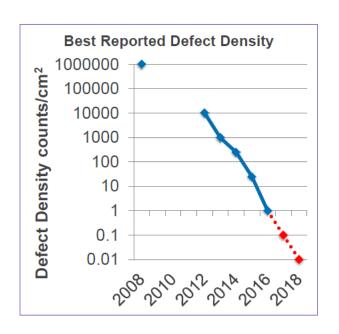

## DSA Defectivity – OK to support Neuromorphic Products now?

#### **DSA Defectivity**

Source: "DSA: How far have we come and how much further is left to go?" Darron Jurajda, Brewer Science, 2016

#### **Defectivity Industry Milestones**

- 2008 0.01% or 10<sup>6</sup> cm<sup>-2</sup>

- 2012 >10,000 cm<sup>-2</sup>

- 2013 Process monitor data first reported, 979 cm<sup>-2</sup>

- 2014 ~200 cm<sup>-2</sup> (LiNe flow), 270 cm<sup>-2</sup> (LETI contacts)

- 2015 24 cm<sup>-2</sup> (LiNe flow golden performance)

- 2016 ~0 cm<sup>-2</sup> (LETI, hole open yield, 0.01 mm<sup>2</sup> inspection area)

- Two more orders of magnitude needed to hit industry target of 0.01 defects cm<sup>-2</sup>

Tada, et. al., Macromolecules, 41, 9267-9276, (2008) Benchera, et. al, SPIE 2012 Caoa. et. al. SPIE 2013 Gronheid, et. al, SPIE 2014 Argoud, et. al, SPIE 2014 Pathangi,, et. al, SPIE 2015

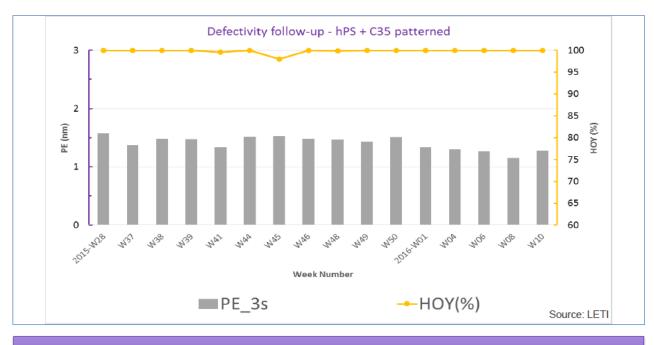

## DSA Defectivity— OK to support Neuromorphic Products now?

DSA Pattern Placement and Hole Open Yield

Consistent placement error (PE) and hole open yield (HOY) week to week

Source: "DSA: How far have we come and how much further is left to go?"

Darron Jurajda, Brewer Science, 2016

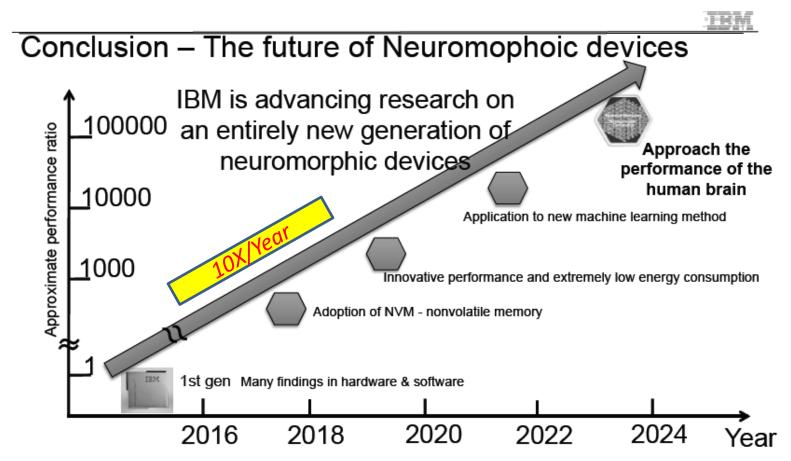

### 2024 - WOW!

From "Neuromophic device for Automotive" by Yoshifumi Sakamoto, Engineering and Cognitive Innovation, IBM Japan, LTD, email: <a href="mailto:sakay@jp.ibm.com">sakay@jp.ibm.com</a>

## Defects – If you cannot beat them – Join them

Loihi simulates a total of 130,000 neurons and 130 million synapses, all capable of communicating with each other... comparable to some small insects. For example, a common fruit fly, an insect studied for AI research, has about 250,000 neurons and 10 million synapses. ...human brain - 100 billion neurons,

https://www.extremetech.com/computing/256467-intel-unveils-new-neuromorphic-self-learning-chip-codenamed-loihi

CPU – Defect Intolerant – Traditional Litho NMU- Defect Tolerant – Minimal Cost Litho

## Defects: If you cannot beat them – join them

Von Neumann Computing will eventually hit scaling wall as defectivity requirements will reach  $< 10^{-14}$ /chip features for overall 0.01/cm<sup>2</sup> defects/layer on a wafer. Neuromorphic Computing can tolerate up to  $4*10^{-1}$  defects per network. Neuromorphic Computing defect tolerance will enable continuation of Moore's Law by augmenting Von Neumann Control parts on the same 2 chip part.

Neuromorphic Computing is expected to be Artificial Intelligence workhorse.

IDC forecasts Global Revenue for Cognitive and AI Systems going from \$18B in 2017 to \$46B in 2020 and Global Cognitive and AI Systems Spending annual growth rate (CAGR) of 54.4% through 2020. Word of caution: AI is at the top of Gartner Hype Cycle now.

Collaboration between Technologists and Computer Architects is needed to create compelling computing products that take advantage of defect tolerant manufacturing.

Directed Self Assembly and NanoImprint Lithography are in a good position to support Neuromorphic Computing parts patterning to provide necessary means to enable Moore's Law beyond capabilities of conventional Lithography

## Thank you for your attention!

Time for Questions

### **Presentation Format**

- Most of the information to be presented are from my previous public talks approved by my former employer, Intel, for external presentation and publications. Those foils will be copied "as is" and will have Intel logo, colored background and information on where and when those were presented.

- Foils made for this presentation will be on simple white background and will have no Intel logo.

- Multiple foils will be using materials presented or published by others during 2015-2018 and will have its source shown on the foil. My additions to those, if any, will be in italic red.